ESP-IDF Introduction#

The ESP-IDF (Espressif IoT Development Framework) is the official operating system and development framework for the Espressif Systems SoCs. It provides a comprehensive environment for building IoT applications with robust networking, security, and reliability features.

The ESP-IDF framework includes FreeRTOS, enabling developers to build real-time, multitasking applications. It provides a comprehensive set of libraries, tools, and documentation, serving as the foundation for development on Espressif devices.

ESP-IDF includes more than 400 examples, covering a wide range of use cases and helping developers quickly get started on their projects.

Architecture#

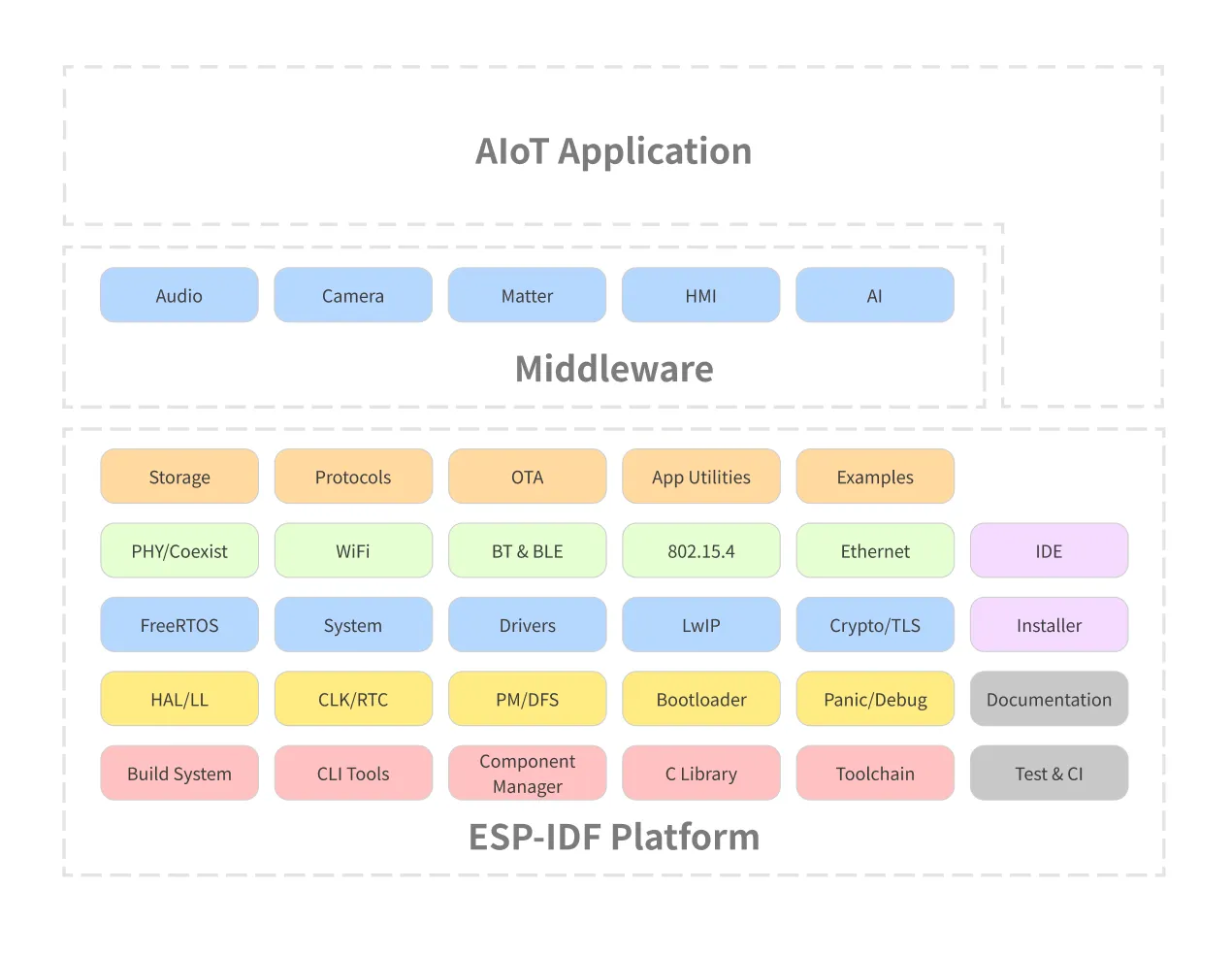

The ESP-IDF platform architecture is mainly divided into 3 layers:

- ESP-IDF platform

- Contains the core components required and the operating system. Includes the FreeRTOS, drivers, build system, protocols, etc.

- Middleware

- Adds new features to ESP-IDF, for example the audio framework and HMI. In this workshop, we won’t use them.

- AIoT Application

- Your application.

Fig.1 - ESP-IDF High level Overview

All the necessary building blocks for your application will be included in the ESP-IDF platform. ESP-IDF is constantly developing, growing, and improving; acquiring new features and supporting more Espressif cores. Visit the ESP-IDF project on GitHub to get the updated list of supported versions and the maintenance period.

Main ESP-IDF blocks#

As mentioned, ESP-IDF is built on FreeRTOS and contains several libraries. The main libraries you will include in your projects are:

- FreeRTOS (

freertos): lightweight, real-time operating system kernel designed for embedded devices, providing multitasking capabilities through preemptive scheduling, task management, and inter-task communication. - Drivers (

esp_driver_xxx): libraries for driving peripherals. - Protocols (

esp_http,esp-tlsetc.): libraries implementing protocols.

During the assignments, you will learn how to include both internal libraries provided by ESP-IDF and external libraries. ESP-IDF also offers a convenient system for managing external dependencies, known as components.

Components#

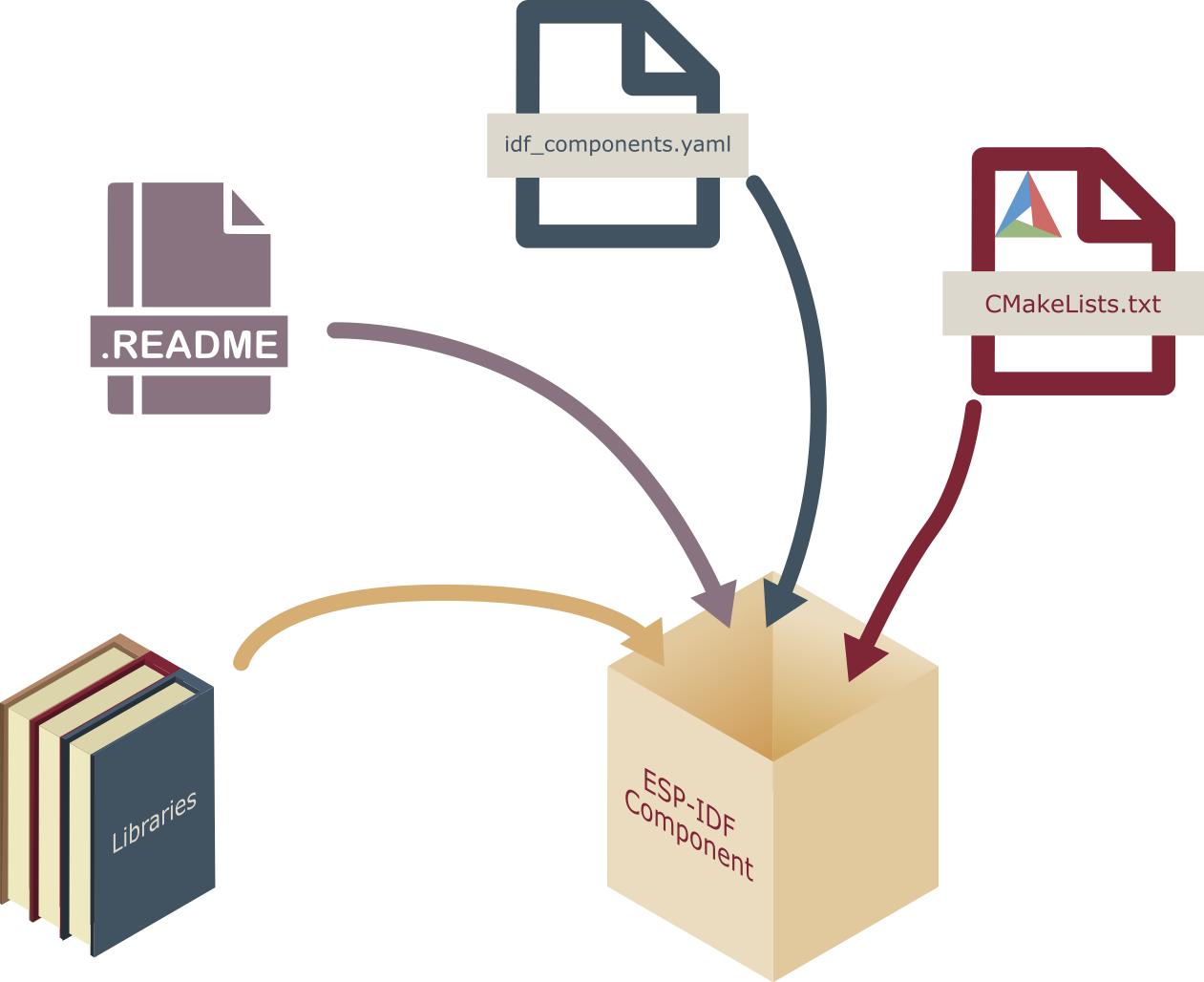

Components are packages that include libraries along with additional files for dependency management, metadata, and configuration.

Fig.2 - ESP-IDF Components

They are used to add new features such as sensor drivers, communication protocols, board support packages, and other functionalities not included in ESP-IDF by default. Some components are already integrated into example projects, and ESP-IDF itself adopts the external component model to promote modularity.

Using components enhances maintainability and accelerates development by enabling code reuse and sharing across multiple projects.

If you want to create and publish your own component, we recommend that you watch the talk DevCon23 - Developing, Publishing, and Maintaining Components for ESP-IDF or read the How to create an ESP-IDF component article.

You can also find components by browsing our ESP Registry platform.

In assignment 3.2, you will have a chance to create your own component and use it in your project.

Frameworks#

Also, ESP-IDF serves as the basis for several other frameworks, including:

- Arduino for Espressif

- ESP-ADF (Audio Development Framework): Designed for audio applications.

- ESP-WHO (AI Development Framework): Focused on face detection and recognition.

- ESP-RainMaker: Simplifies building connected devices with cloud capabilities.

- ESP-Matter SDK: Espressif’s SDK for Matter is the official Matter development framework for ESP32 series SoCs.

To see all the supported frameworks, please visit our GitHub organization page.

ESP-IDF Development#

In addition to libraries, ESP-IDF includes the necessary tools to compile, flash, and monitor your device.

You can develop applications for Espressif devices using any plain text editor, such as Gedit or Notepad++, by following the manual installation guide provided in Espressif’s documentation.

However, for this workshop, we will use an IDE (Integrated Development Environment) to streamline both development and setup. Espressif supports several IDEs, but we will focus on Visual Studio Code (VS Code). Espressif provides an official VS Code extension called ESP-IDF, which enables you to develop, compile, flash, and debug your projects directly within the editor.

To give you an idea, the ESP-IDF VS Code Extension manages the toolchain and gives you some useful commands which we will use later, such as:

> ESP-IDF: Build Your Project> ESP-IDF: Set Espressif Device Target> ESP-IDF: Full clean project

The character > indicates VS Code Command Palette, which can be opened by pressing F1 or Ctrl+Shift+P (or Cmd+Shift+P).

All these commands are wrappers around the main ESP-IDF front-end tool which is idf.py.

Hardware used in this workshop#

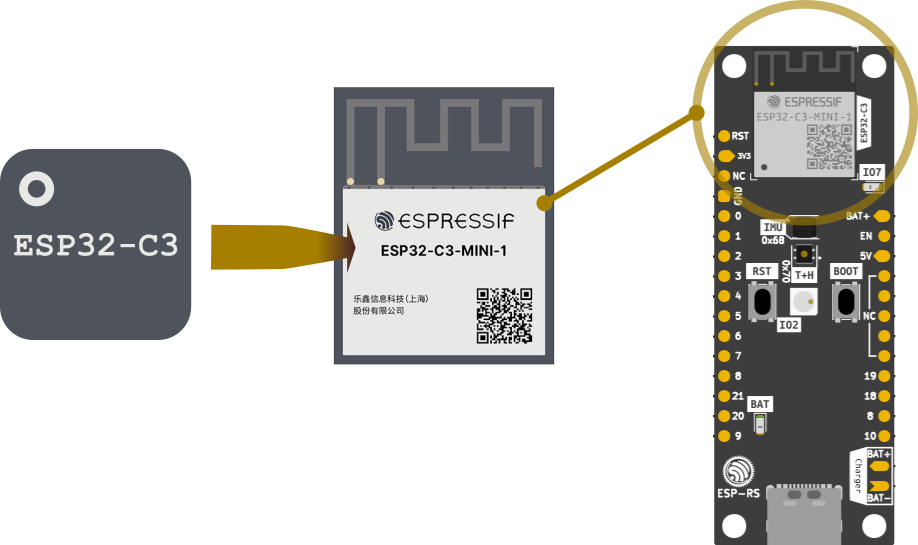

In this workshop, you will use a development kit (devKit) based on an Espressif SoC. Espressif SoCs are typically integrated as modules in final products. A development kit is a simple board that includes an Espressif module, the necessary supporting components, and easily accessible pins for prototyping.

Fig.3 - SoC, module, and devKit

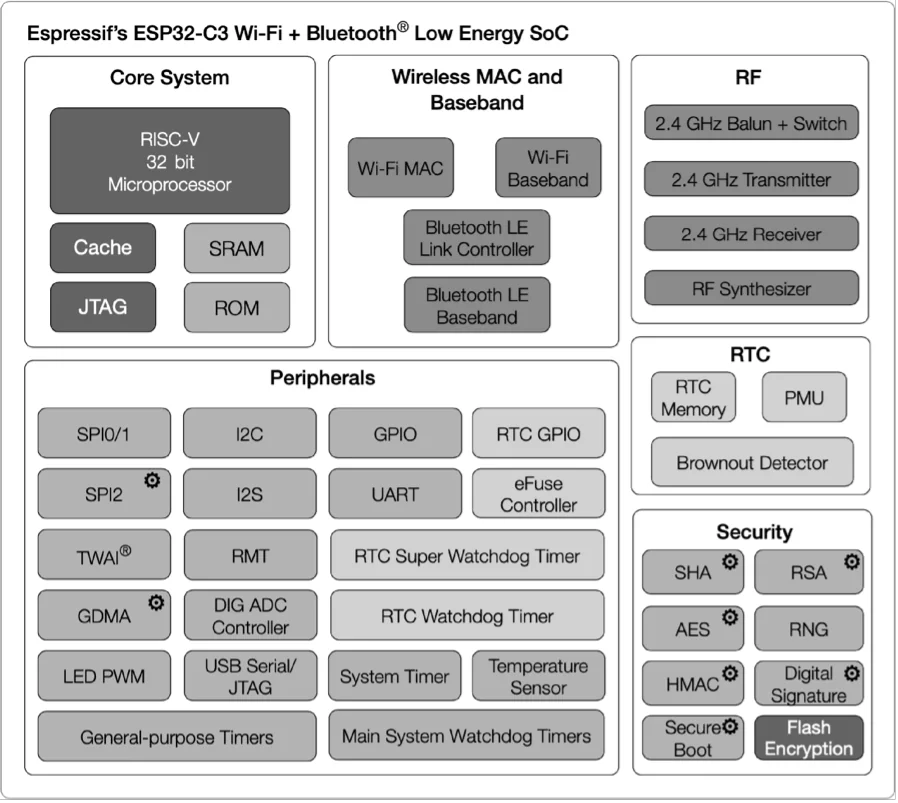

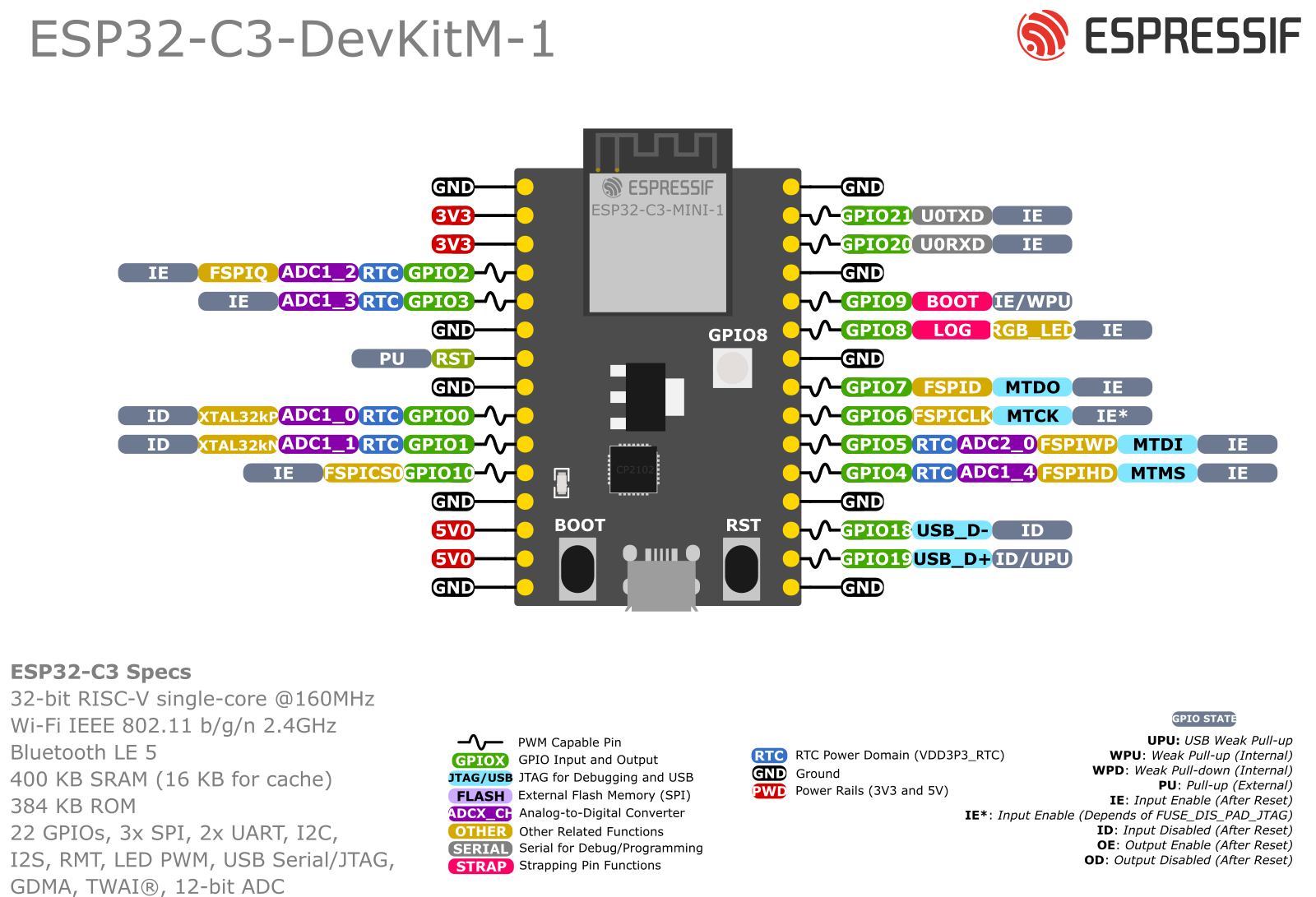

ESP32-C3 SoC#

ESP32-C3 SoC is an SoC equipped with a 32-bit RISC-V processor, supporting 2.4 GHz Wi-Fi and Bluetooth LE connectivity. The functional block diagram for ESP32-C3 is shown below

ESP32-C3 Block Diagram

ESP32-C3 has the following features:

32-bit RISC-V single-core processor @ 160 MHz.

Wi-Fi subsystem

Supports Station mode, SoftAP mode, SoftAP + Station mode, and promiscuous mode.Bluetooth LE subsystem

Supports Bluetooth 5 and Bluetooth mesh.Integrated memory

400 KB SRAM and 384 KB ROM on the chip, external flash connection capabilitySecurity mechanisms

Cryptographic hardware accelerators, encrypted flash, secure bootloaderRich set of peripheral interfaces

The 22 programmable GPIOs can be configured flexibly to support LED PWM, UART, I2C, SPI, I2S, ADC, TWAI, RMT, and USB Serial/JTAG applications.

The ESP32-C3 series of chips has several variants, including the version with in-package SPI flash. You can find them on the ESP32-C3 Series Comparison section of the datasheet. ESP8685 is a small package version of ESP32-C3.

ESP32-C3-Mini-1-N4 Module#

In addition to SoCs, Espressif offers modules, which integrate an SoC, additional flash, (optionally) PSRAM memory, and a PCB antenna or an antenna connector. The main advantage of modules is not only their ease of use but also a simplified certification process.

The most common ESP32-C3 module is the ESP32-C3-MINI-1-N4. It includes 4MB of flash.

ESP32-C3 DevKit#

ESP32-C3-Devkit-M top view

Schematics#

You can find the board schematic on the KiCad Libraries GitHub Repository.

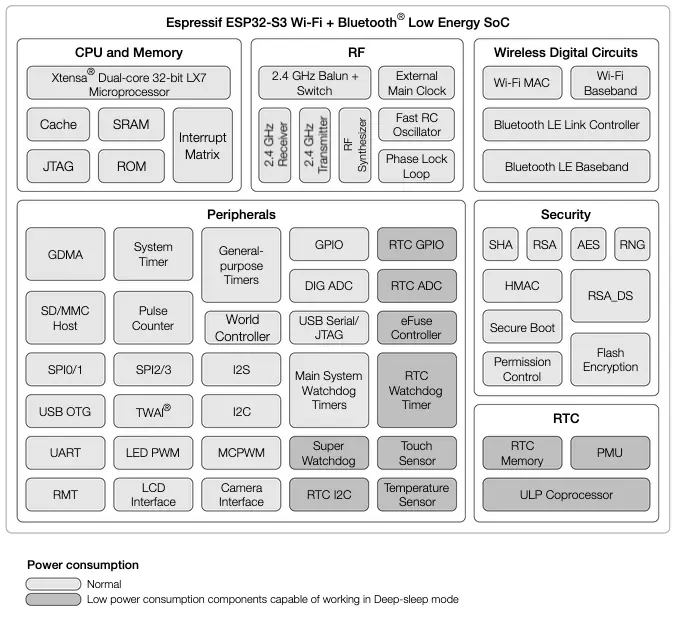

ESP32-S3 SoC#

ESP32-S3 SoC is a highly integrated SoC equipped with dual-core 32-bit Xtensa LX7 processors, supporting 2.4 GHz Wi-Fi and Bluetooth LE connectivity. The functional block diagram for ESP32-S3 is shown below.

ESP32-S3 Block Diagram

ESP32-S3 has the following features:

Dual-core 32-bit Xtensa LX7 processors @ up to 240 MHz.

A Wi-Fi subsystem

Supports Station mode, SoftAP mode, SoftAP + Station mode, and promiscuous mode.A Bluetooth LE subsystem

Supports Bluetooth 5.Integrated memory

512 KB SRAM and 384 KB ROM on the chip, external flash and PSRAM connection capabilitySecurity mechanisms

Cryptographic hardware accelerators, encrypted flash, secure bootloader, digital signatureA rich set of peripheral interfaces

The 45 programmable GPIOs can be configured flexibly to support LED PWM, UART, I2C, SPI, I2S, ADC, DAC, TWAI, RMT, USB OTG, and USB Serial/JTAG applications.AI acceleration

Vector instructions for accelerating neural network computing and signal processing workloads.

The ESP32-S3 series of chips has several variants, including versions with in-package SPI flash and PSRAM. You can find them in the ESP32-S3 Series Comparison section of the datasheet.

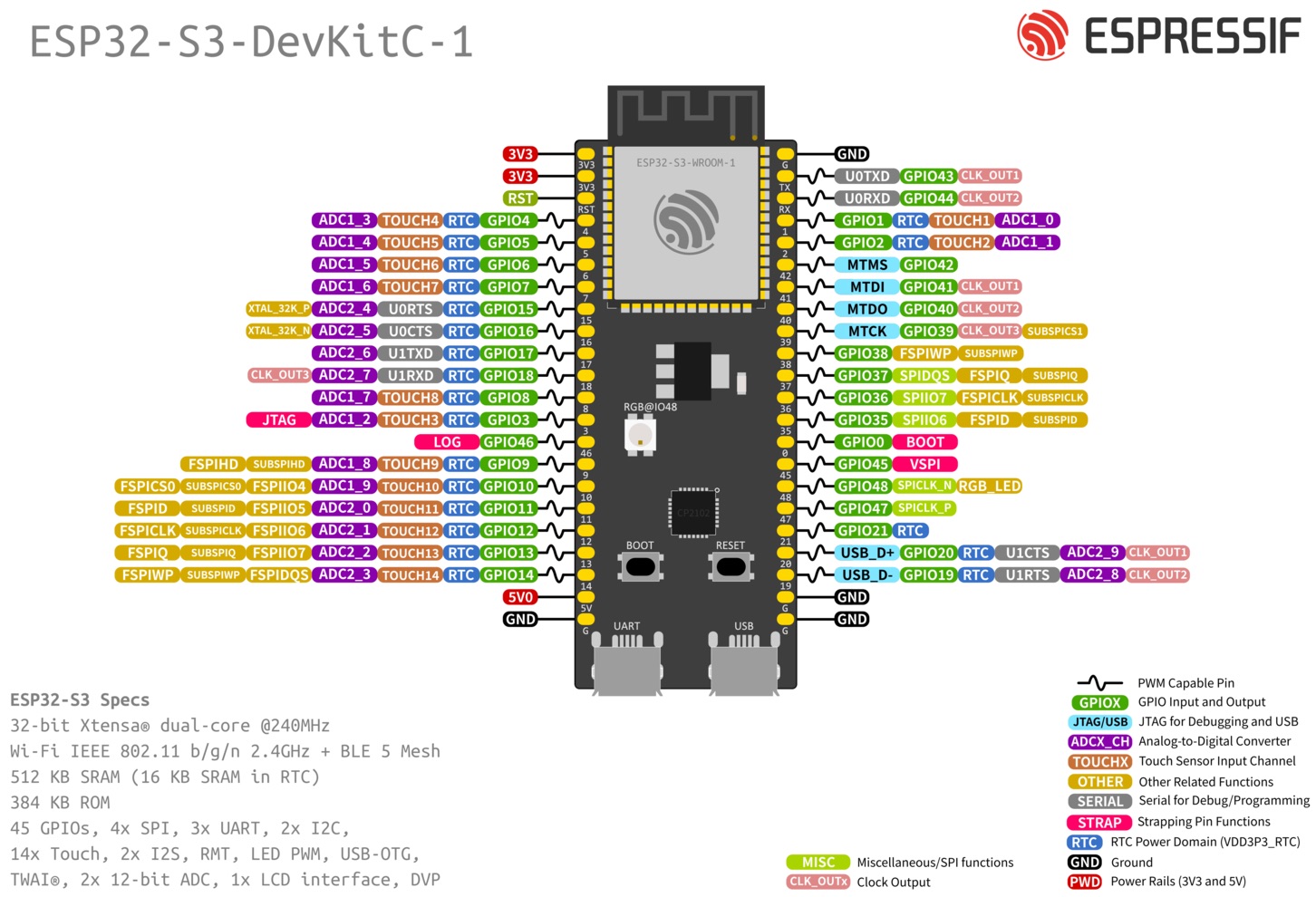

ESP32-S3-WROOM-1 Module#

In addition to SoCs, Espressif offers modules, which integrate an SoC, additional flash, (optionally) PSRAM memory, and a PCB antenna or an antenna connector. The main advantage of modules is not only their ease of use but also a simplified certification process.

A common module is the ESP32-S3-WROOM-1. Depending on the variant, it includes different configurations of flash and PSRAM.

ESP32-S3 Development board#

ESP32-S3-DevKitC-1 top view

Schematics#

You can find the board schematic on the ESP32-S3-DevKitC-1 Documentation page.

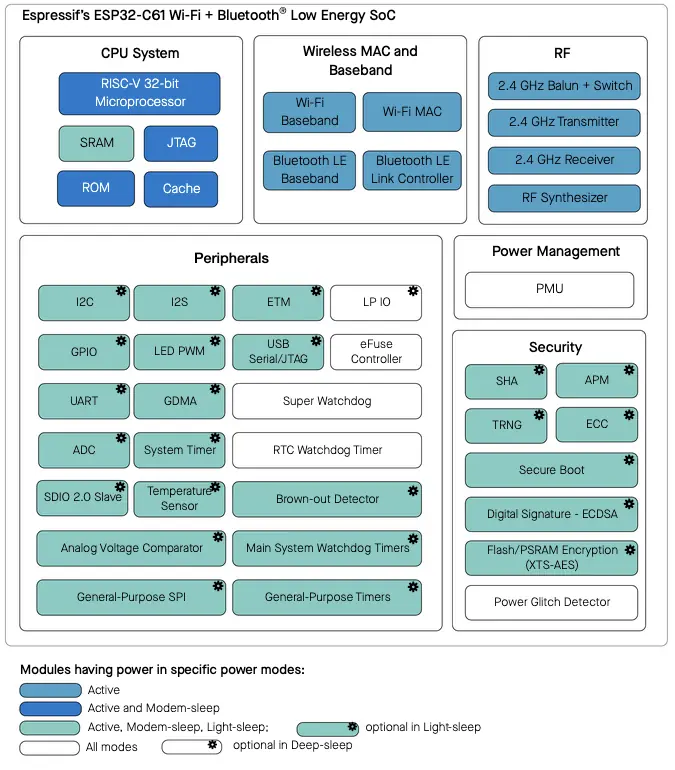

ESP32-C61 SoC#

ESP32-C61 SoC is designed to deliver affordable Wi-Fi 6 connectivity, equipped with a 32-bit RISC-V processor, supporting 2.4 GHz Wi-Fi 6 and Bluetooth 5 (LE) connectivity. The functional block diagram for ESP32-C61 is shown below.

ESP32-C61 Block Diagram

ESP32-C61 has the following features:

A 32-bit RISC-V single-core processor @ 160 MHz.

A Wi-Fi 6 subsystem

Supports 20 MHz bandwidth for 802.11ax mode with OFDMA and MU-MIMO, and 20/40 MHz bandwidth for 802.11b/g/n mode. Includes Target Wake Time for ultra-low power applications.A Bluetooth LE subsystem

Supports Bluetooth 5 (LE) with long-range operation through advertisement extension and coded PHY, and Bluetooth Mesh 1.1 protocol.Integrated memory

320 KB SRAM and 256 KB ROM on the chip, works with Quad SPI flash and supports in-package PSRAM with Quad SPI up to 120 MHzSecurity mechanisms

Cryptographic hardware accelerators, secure boot, flash and PSRAM encryption, ECDSA-based digital signature peripheral, Trusted Execution Environment (TEE)A rich set of peripheral interfaces

Programmable GPIOs can be configured flexibly to support LED PWM, UART, I2C, SPI, I2S, ADC, LP IO, TWAI, RMT, and GDMA. Specialized peripherals include Event Task Matrix (ETM) and Analog Voltage Comparator.

The ESP32-C61 series of chips has several variants with different configurations. You can find them in the ESP32-C61 Series Comparison section of the datasheet.

ESP32-C61-WROOM-1 Module#

In addition to SoCs, Espressif offers modules, which integrate an SoC, additional flash, (optionally) PSRAM memory, and a PCB antenna or an antenna connector. The main advantage of modules is not only their ease of use but also a simplified certification process.

A common module is the ESP32-C61-WROOM-1. Depending on the variant, it includes different configurations of flash and PSRAM.

ESP32-C61 Development board#

ESP32-C61-DevKitC-1 top view

If you’re curious about how to interpret the module part number, you can check the article Espressif part numbers explained: A complete guide - Modules on the Espressif Developer Portal .

Conclusion#

Now that we have a high-level overview of both hardware and firmware, we’re ready to start the first assignment.

Next Step#

Next Assignment → assignment 1.1